- 您现在的位置:买卖IC网 > Sheet目录3818 > PIC18F4620-I/ML (Microchip Technology)IC MCU FLASH 32KX16 44QFN

PIC17C4X

DS30412C-page 120

1996 Microchip Technology Inc.

CPFSLT

Compare f with WREG,

skip if f < WREG

Syntax:

[

label ] CPFSLT

f

Operands:

0

≤ f ≤ 255

Operation:

(f) –

(WREG),

skip if (f) < (WREG)

(unsigned comparison)

Status Affected:

None

Encoding:

0011

0000

ffff

Description:

Compares the contents of data memory

location 'f' to the contents of WREG by

performing an unsigned subtraction.

If the contents of 'f' < the contents of

WREG, then the fetched instruction is

discarded and an NOP is executed

instead making this a two-cycle instruc-

tion.

Words:

1

Cycles:

1 (2)

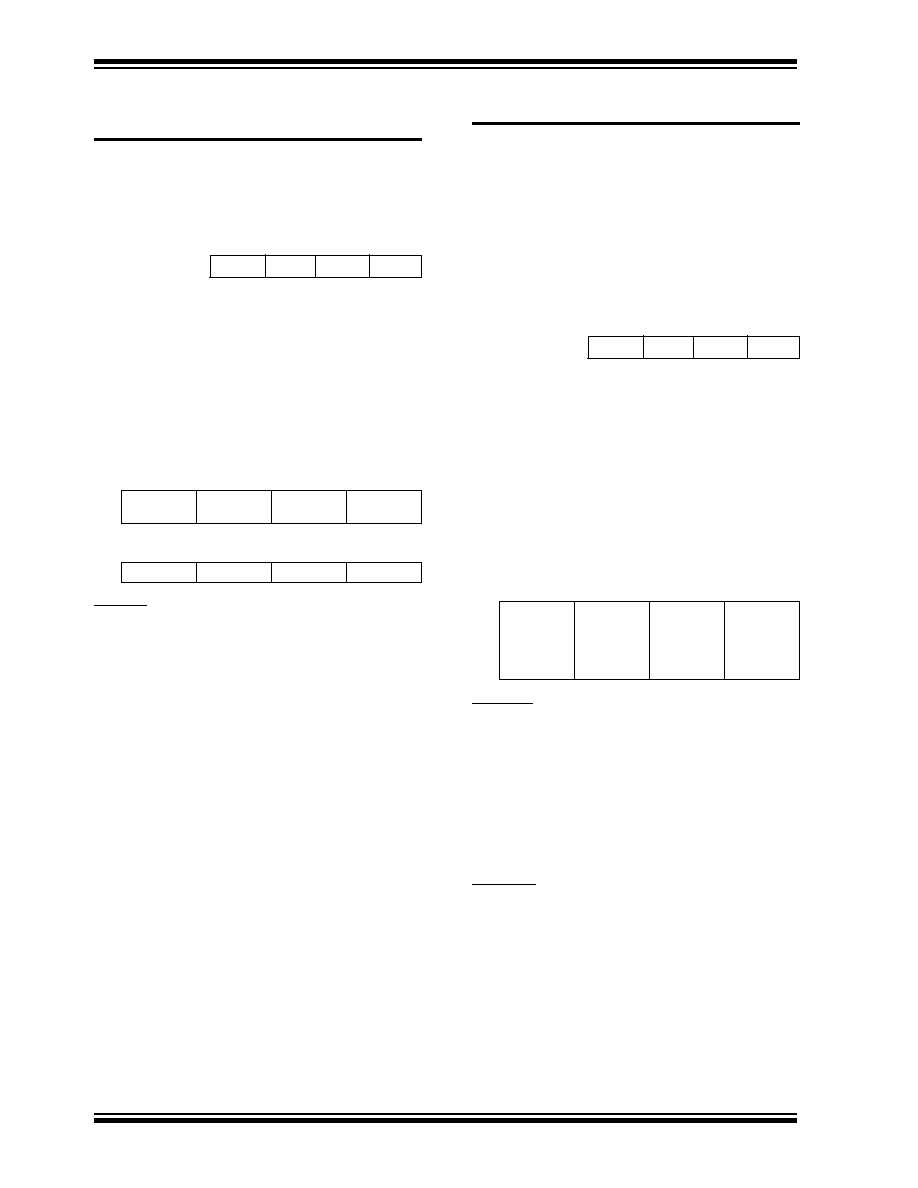

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

register 'f'

Execute

NOP

If skip:

Q1

Q2

Q3

Q4

Forced NOP

NOP

Execute

NOP

Example:

HERE

CPFSLT REG

NLESS

:

LESS

:

Before Instruction

PC

=

Address (HERE)

W=

?

After Instruction

If REG

<

WREG;

PC

=

Address (LESS)

If REG

≥

WREG;

PC

=

Address (NLESS)

DAW

Decimal Adjust WREG Register

Syntax:

[

label] DAW

f,s

Operands:

0

≤ f ≤ 255

s

∈ [0,1]

Operation:

If [WREG<3:0> >9] .OR. [DC = 1] then

WREG<3:0> + 6

→ f<3:0>, s<3:0>;

else

WREG<3:0>

→ f<3:0>, s<3:0>;

If [WREG<7:4> >9] .OR. [C = 1] then

WREG<7:4> + 6

→ f<7:4>, s<7:4>

else

WREG<7:4>

→ f<7:4>, s<7:4>

Status Affected:

C

Encoding:

0010

111s

ffff

Description:

DAW adjusts the eight bit value in

WREG resulting from the earlier addi-

tion of two variables (each in packed

BCD format) and produces a correct

packed BCD result.

s = 0:

Result is placed in Data

memory location 'f' and

WREG.

s = 1:

Result is placed in Data

memory location 'f'.

Words:

1

Cycles:

1

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

register 'f'

Execute

Write

register 'f'

and other

specied

register

Example1:

DAW

REG1, 0

Before Instruction

WREG

=

0xA5

REG1

=

??

C=

0

DC

=

0

After Instruction

WREG

=

0x05

REG1

=

0x05

C=

1

DC

=

0

Example 2:

Before Instruction

WREG

=

0xCE

REG1

=

??

C=

0

DC

=

0

After Instruction

WREG

=

0x24

REG1

=

0x24

C=

1

DC

=

0

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC24HJ256GP210-I/PT

IC PIC MCU FLASH 128KX16 100TQFP

PIC24HJ128GP310A-I/PF

IC PIC MCU FLASH 128KB 100-TQFP

DSPIC33FJ128GP310-I/PF

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SO

IC MCU OTP 8KX14 PWM 28SOIC

DSPIC33FJ128MC510-I/PT

IC DSPIC MCU/DSP 128K 100TQFP

PIC16C66-20I/SP

IC MCU OTP 8KX14 PWM 28DIP

PIC18LF2620-I/SP

IC MCU FLASH 32KX16 28SDIP

PIC16F877-04I/P

IC MCU FLASH 8KX14 EE 40DIP

相关代理商/技术参数

PIC18F4620-I/P

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 DIP40

PIC18F4620-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620-I/PT

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4620 TQFP44

PIC18F4620T-I/ML

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4620T-I/PT

功能描述:8位微控制器 -MCU 64KB 3968 RAM 36 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/ML

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4680-E/P

功能描述:8位微控制器 -MCU 64KB 3328 RAM w/ECAN RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT